测试

揭秘半导体制造全流程

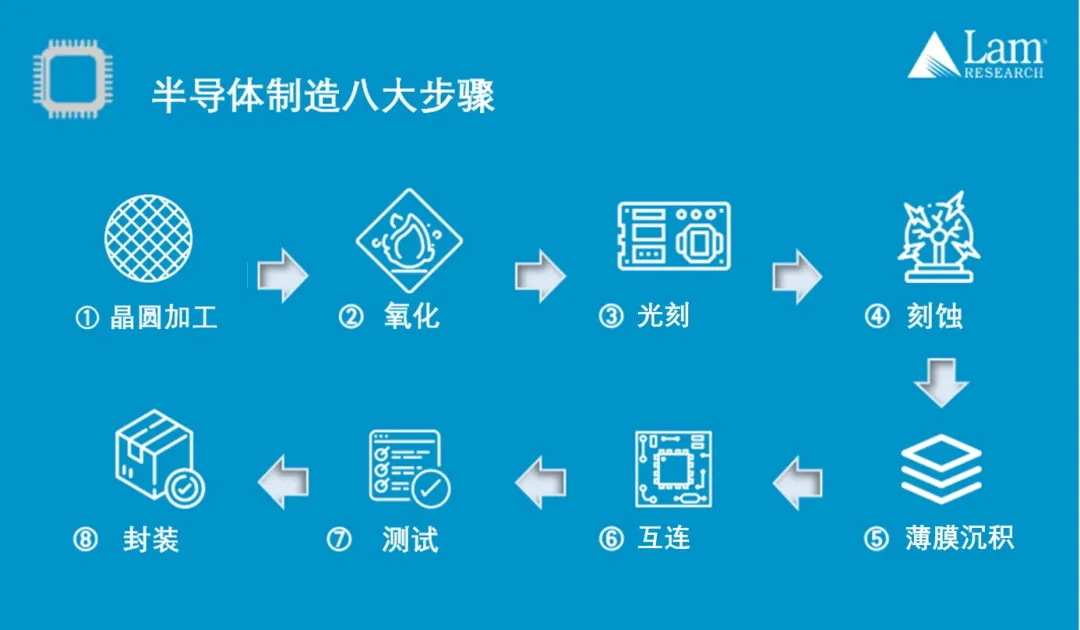

当听到“半导体”这个词时,你会想到什么?它听起来复杂且遥远,但其实已经渗透到我们生活的各个方面:从智能手机、笔记本电脑、信用卡到地铁,我们日常生活所依赖的各种物品都用到了半导体。每个半导体产品的制造都需要数百个工艺,泛林集团将整个制造过程分为八个步骤:晶圆加工-氧化-光刻-刻蚀-薄膜沉积-互连-测试-封装。为帮助大家了解和认识半导体及相关工艺,我们将以三期微信推送,为大家逐一介绍上述每个步骤。

你真的懂IC测试吗?

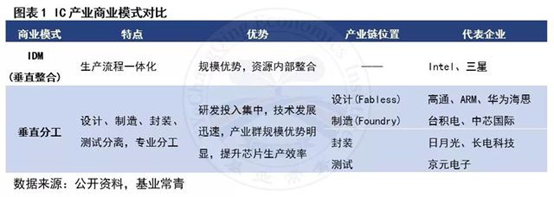

来源:内容来自「基业常青经济研究院 」,作者:陈凯,谢谢。从IDM到垂直分工,IC产业专业化分工催生独立测试厂商出现。集成电路产业从上世纪60年代开始逐渐兴起,早期企业都是IDM运营模式(垂直整合),这种模式涵盖设计、制造、封测等整个芯片生产流程,这类企业一般具有规模庞大、技术全面、积累深厚的特点,如Intel、三星等。随着技术升级的成本越来越高以及对IC产业生产效率的要求提升,促使整个产业逐渐向

半导体厂商如何做芯片的出厂测试?

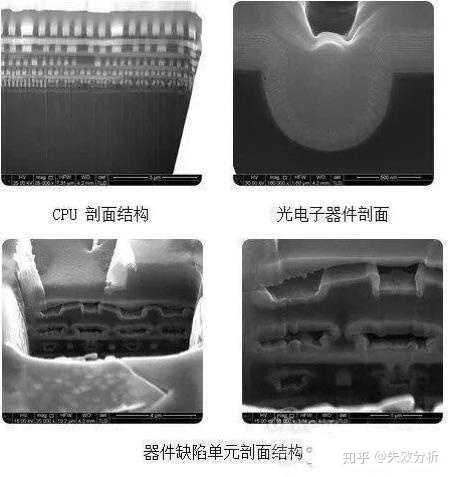

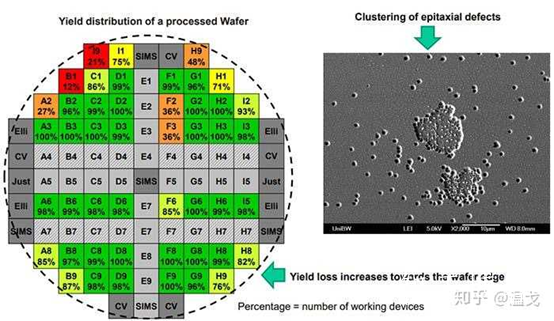

我觉得这个问题就是为我量身定制的!作为前Teradyne ATE工程师,现AMD DFT+数字IC设计工程师,以亲身项目经验,来谈谈这个问题。先来说一下完整的测试流程,再针对题主的两个问题回答一下。一、芯片测试概述芯片测试分两个阶段,一个是CP(Chip Probing)测试,也就是晶圆(Wafer)测试。另外一个是FT(Final Test)测试,也就是把芯片封装好再进行的测试。CP测试的目的就