经典:CMOS寄生特性之SnapBack/Latchup (转)

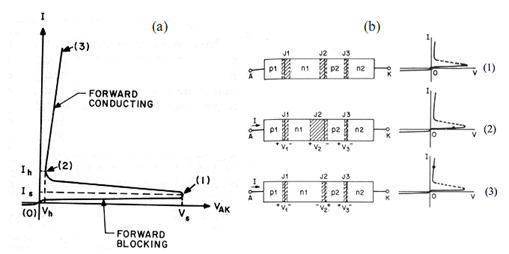

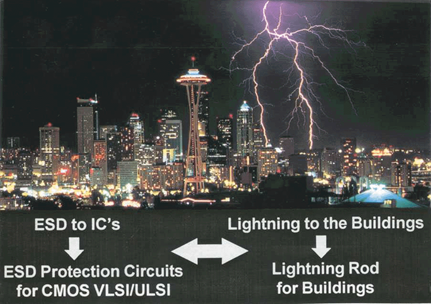

本文转自芯苑,ic-garden.cn (由于芯苑会经常关闭站点,故转载存留)Snap-Back和Latch-up应该是CMOS寄生特性里面最经典的理论了,其实他两个是同一个东西,都是NMOS和PMOS的寄生三极管等效电路开启进入正反馈状态下的回路导通状态,叫做Snap-back是因为当寄生回路触发导通之后,会迅速进入低阻状态,所以I-V曲线迂回呈现负阻状态,所以叫做Snap-back(侧重工作区