SOI

晶圆制备–绝缘体上硅(SOI) (转)

最近半导体界比较hot的新闻比较多,抛开我们公司(tsmc, 2330)和友公司的10nm和7nm互相宣传外,另外一个新闻便是GlobalFoundry(俗称女朋友)7月14日高调宣布22nm的FD-SOI制程的“22FDX"制程平台。这可是全球首家,当制程节点走向28nm以下时就不得不进入FinFET时代,这可是结构的变化,很多器件模型可谓翻天覆地的变化,设计难度和成本增加很多很多。如果有一家能

FD-SOI到底是什么?

来源:全球半导体观察当半导体工艺制程发展到22纳米时,为了满足性能、成本和功耗要求,延伸发展出来FinFET和FD-SOI两种技术。由于半导体龙头厂商英特尔主导推广FinFET技术,并得到晶圆代工大厂台积电的支持,使得FinFET技术大行其道。不过,最近几年SOI制程工艺越来越受业界关注,其技术优势和应用前景也越发地被看好。格芯、三星、索尼、意法、芯原微电子等产业厂商在SOI技术上的投入越来越大。

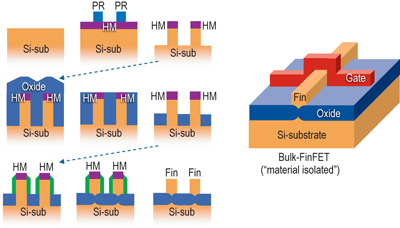

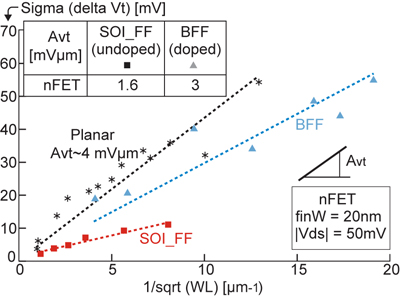

“芯”无远虑,必有近忧 ----FD-SOI与FinFET工艺,谁将接替Bulk CMOS?

“传统Bulk CMOS工艺技术将在20nm走到尽头,必须用创新的思路和方法寻找新的替代工艺。”----IBS主席兼 CEO Handel Jones现在,大量IC采用体硅CMOS(Bulk CMOS)工艺技术实现,这是一种制造成本低、性能较高和具备不错低功耗性能的成熟技术,但是,当工艺节点升级到20nm左右时,Bulk CMOS将无法获得等比例缩小的性能、成本和功耗优势,很多业者认为B

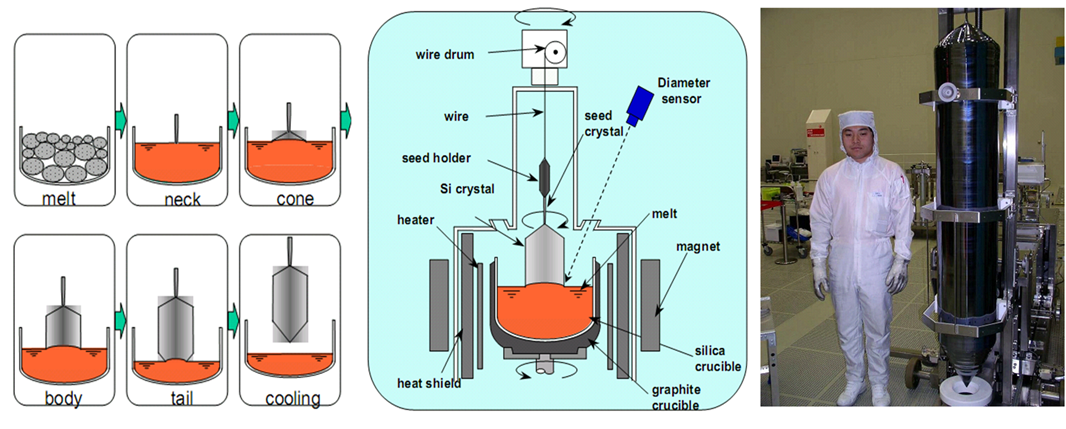

晶圆制备–如何从沙子到wafer? (转)

我们所讲的半导体制造,它的载体一定是晶圆(Wafer),这个东西是怎么来的?我们今天就来好好讲讲。前面讲N-Si和P-Si掺杂的时候讲过了,我们的Si一定都是单晶晶格的,而掺杂的原子必须跑到它的晶格上与Si形成共用电子对的共价键后多出电子或空穴而参与导电,如果我们用了多晶或者非晶,这些没有规律的结构导致我们无法掌控他的载流子迁移率所以无法控制它的电性,所以我们的wafer一定要是是Si的单晶。当然