本文转自芯苑,ic-garden.cn (由于芯苑会经常关闭站点,故转载存留)BCD - The Most Interesting Process Technology You Haven't Heard Of")

从Marketing和Demand来讲,最近这几年PMIC非常火热的驱动力主要来自Smartphones、Tablet等消费类(2015年有10亿只Smartphone和一个亿的tablet)。每个手机的components都需要一个PMIC,比如AP处理器,Baseband处理器,Display Driver,Charger等等,所以可想而知PMIC的市场该有多大?根据IHS Research预计,2016年PMIC的shipping量(包括Converter, Controller, Voltage regulator, Battery management等)大约是35billion USD,到2019年会上升到40billion USD,主要的region依然是中国和美国。而Technavio's market research预估到2020年全世界BCD技术的年复合增长率会达到7%以上。

从厂商来讲,BCD技术主要起源于1980年代,但是由于制程过于复杂(niche technologies),所以这种技术早期只有IDMs(Integrated-Device-Manufacturer)可以提供,比如主流的TI、ST、Infineon,还有其他如Renesas, NXP, Mitsubishi, Maxim Integrated, and ON Semiconductor等,随着Foundry技术能力的提升,主要的Vendor有TSMC和GF,还有Allegro MicroSystems、Jazz Semiconductor、Magnachip、Tower Jazz以及United Microelectronics。

好了,扯了一大堆没用的,还是来点技术干货吧!

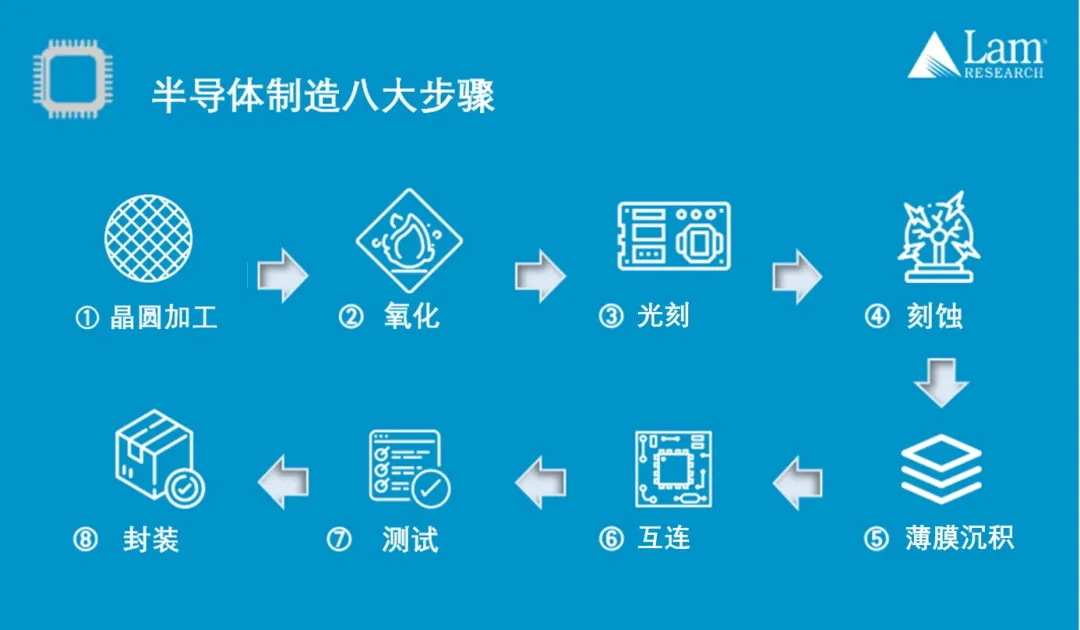

我们知道在Power Management的前身是Power IC,所以重点在于“Management”。早期的Power IC功能比较单一,只能实现控制、转换功能(比如AC-DC, DC-DC等),而到了Power Management IC时代,则需要增加Multi-channel DC-DC或LDO,而且增加DSP以及eNVM等功能,所以更进一步变成smart power。

先讲讲BCD里面的BJT吧,它主要用来做Analog处理,记住不是power哦,power是靠DMOS的。为什么要用BJT呢?主要是利用它的精准的Bandgap Vref。记得以前拉扎维的模电教材有一个经典的叫做带隙基准,其实他就是Bandgap。它主要的原理就是可以实现一个与温度无关的电压(NPN的Vbe是负温度系数,而BJT的等效热电压Vt=kT/e是正温度系数,这样就可以相互抵消从而实现温度无关的基准电压),用这个电压作为模拟电路的参考电压来提高精准度。所以一般BCD里面Bipolar特别key的是NPN管。但是有一点要记住,如果BJT的Hfe太小则表示Ib比较大,那么Vbe的温度系数会发生变化,所以这个基准电压也会发生变化的。

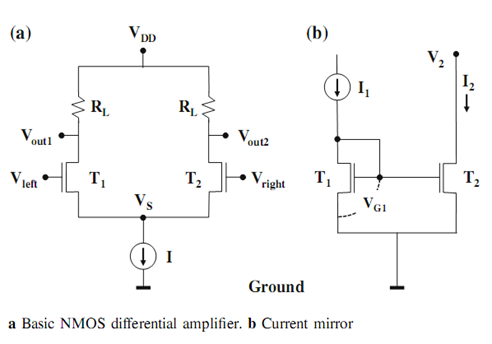

其次是CMOS,主要是做数字信号处理,就是一般的Logic部分,当然也有一部分CMOS可以用来做Analog信号处理,那么它和digital就不一样了,主要的concern是Noise。而这个Noise一般来自于两个,一个是相邻周边器件或导线电荷干扰,另一种则是来自于器件本身的Flicker噪声,而前者只能靠隔离(Trench or Deep-Well)后者需要Trap或Gettering来实现。现在主流的Sensor有很多微弱的信号处理都是需要CMOS的Analog应用,所以low-noise将会是重要的指标之一。比较经典的CMOS在analog应用就是差分放大器和镜像电流源,这里我也不懂就不细说了。

当然CMOS除了Analog应用之外,还有就是RF的应用。

最后是DMOS,当然DMOS包含VDMOS和LDMOS,而BCD里面用到的肯定是LDMOS,因为他要与CMOS集成就无法在背面引电极了。这也是BCD能够处理Power的核心,而对他的要求我前面的文章也有讲解主要就是BV和Rdson,既能抗压也能减小conduction loss和Switch loss。而conduction loss主要来自导通电阻Rdson,而switch loss主要来自于Gate Capacitance (Qg)与Rdson的乘积。当Vg加在Gate上准备开启的时候,因为Gate与Drain、Source之间总会有电容的,而这个电容需要充电时间然后才能通过耦合开启器件,而这个充电时间就是RC-delay咯,所以如果要减小Switch Loss就必须减小栅极电阻以及降低Gate与Source/Drain的电容。一般情况下在一个Power模块中,High-side比较care的是Qg,而Low side一般care的是Ron。

BCD技术的挑战是什么?

1、温度:传统的Logic和analog我们认为几十度(85C)应该足够了,但是BCD因为有了DMOS它的温度一下子就上去了,所以它的reliability评估必须cover高温特性,比如125C~150C。

2、封装:传统的封装都是wire bond或者gold bond,需要基板和molding compound,但是这种封装方式最大的问题就是散热差,你想想你给BCD的芯片裹了那么多层被子,还不得捂死它啊?所以到了BCD时代必须采用CSP(Chip-Scale-Package)封装,这种封装方式的尺寸基本和Die Size相当,后来发展到Wafer-Level CSP,再后来到RDL+Flip Chip封装。(后面再专题学习封装吧~)

发表评论 取消回复