如何查Vt shift的Case?MOSFET开启电压(Vt)的制程因素!(转)

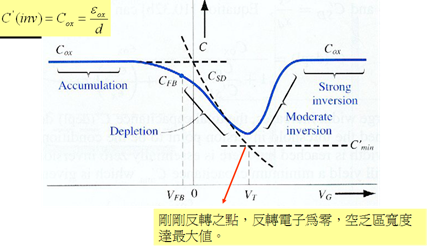

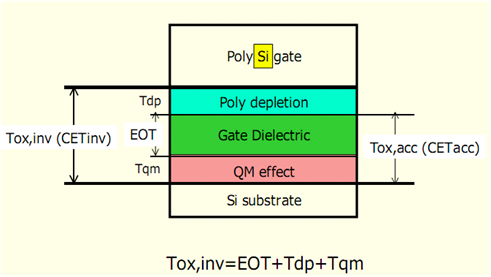

本文转自芯苑,ic-garden.cn (由于芯苑会经常关闭站点,故转载存留)很久没有写文章了,客观原因是电脑坏了,主观原因是不知道写什么。类似我们的学习,我们很想好好学习,很想像某人一样功成名就,每个人都是上进的,科学的方法和明确的计划才是最重要的。看来我的反思如何把《芯苑》走的更远,希望大家能够给我些建议,我自己蠢就得求助你们!好了,先把今天的课题讲完吧,前面很长一段时间都在讲栅极 (栅极材料