本文转自芯苑,ic-garden.cn (由于芯苑会经常关闭站点,故转载存留)

但凡对半导体这个行业有点了解的,应该都懂摩尔定律(Moore's Law),这也是个魔咒。这是70年代Intel创始人Gordon Moore在60年代提出来的黄金定律,被业界遵循为黄金定律,也是从那个年代开始我们世世代代的半导体人都为之疯狂,这就是为什么这个行业的人压力那么大的原因。

--Small is Beautiful!浓缩就是精华!

说起摩尔定律,大家一定比我会背:每18个月(后来修正到18~24个月),单位面积的晶体管数目需要增加一倍,当然换算到Cost就是降低一半了,曾经有人无聊的算过一笔账,如果按照摩尔定律的速度,现在那些奔驰宝马也就几分钱。但是你知道这个定律的描述如何和我们的0.5um、0.35um、0.25um....90um、65um、45nm、28nm等关系吗?我们每个节点都是一个generation,而每个generation如何实现面积减小一半?因为我们需要面积缩小一半,也就是50%,那样边长需要缩小多少?是不是70%?这样才能70%*70%从而达到50%的面积节省,所以就有了0.5um*70%到0.35um,0.18*70%=0.13um就这么来的,简单吧。

当然实际过程中,你们也经常会看到从0.18um会到0.16um,甚至有0.15um,然后才到0.13um,对吧?为什么不直接到跳0.13um呢?因为从0.18um直接到0.13um跨度太大,很多技术挑战不能一下子实践,所以业界都是摸石子过河,先一步步90% shrink,通过shrink发现工艺过程中的问题,逐个解决再最终完成70% shrink。比如当年的0.35um到0.25um的变化就是最经典的,可以说出一箩筐的问题(STI, Poly, GOX, Poly, TiSix都变了)。从0.18um shrink到0.13um最经典的也是OD SiN的pull back,再往下shrunk还有SiN linear等等 (这些我们后面讲flow再跟大家分享)。其实大家自己去看看你们公司的各technology的flow加上你们的聪明才智,应该都能理解的。这就是为什么我让新人学习flow一定要让他们横向比较给我讲为什么。

好了,接下来我们讲一下在制程上,我们除了poly特征尺寸shrink了70%外,还有那些制程参数也必须要shrink。

1) GOX厚度:不管我们怎么shrink,我们要保证的是电流驱动能力,也就是单位宽度下的饱和电流(Ion/W)。为了满足这个那我们的等比例降低GOX厚度,这样才能保证足够的跨导(Gm)来驱动沟道电流。所以知道为啥0.5um时候是120A,到0.35um的时候是70A了吧?

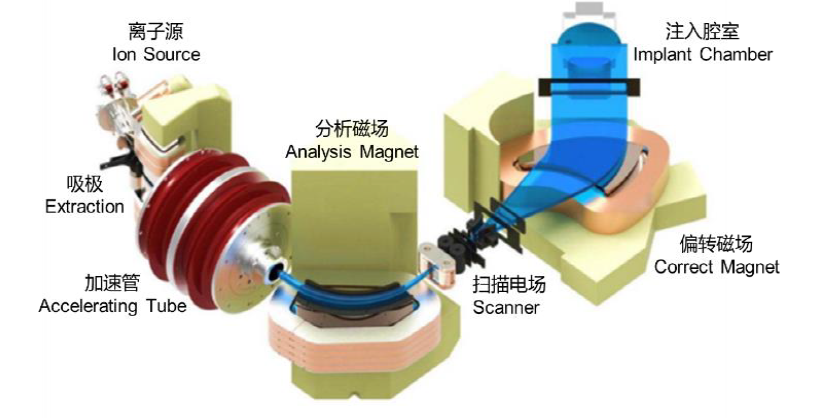

2) Junction深度:因为你的沟道长度shrink了,如果你的节深不变,那横向扩散是不是更加严重?那更容易punch through和DIBL (Drain Induced Barrier Low)了,而且节电容导致的RC delay也会越严重。所以Junction也需要等比例缩小。

3) 隔离区(LOCOS/STI),为了面积,所以所有的平面必须都要等比例缩小,才能保证每个单位晶体管面积缩小,当然包括隔离区了,所以说指甲盖大小的区域真是寸土寸金啊。这就是为什么后来发展到0.25um要用STI制程,再到0.18um要使用bordless contact的原因了。

4) Contact/Via/Metal等互连:曾有人算过,因为互连占用掉的芯片面积将近30%,所以如果互连不等比例缩小,那你肯定也无法降低面积吧。

5) 工作电压(Vcc):如果我的沟道长度都小了,GOX也薄了,你电压不等比例缩小,它也撑不住啊。所以电压也必须要等比例缩小0.5um时候是5V,0.35um的时候是3.3V,0.25um时候是2.5V等等。

6) 工作频率:得益于节深减小,互连减小,所以寄生(parasitic)电容减小,所以频率自然就高了,开关速度也快了。电路速度也就快了。

7) 电阻:这个没办法缩小,因为implant的Si总是会饱和,而且implant的Si即使饱和了也会有70~80ohm/sq,所以只能靠金属硅化物了(TiSix->CoSix->NiSix)

8) 功耗:得益于工作电压(Vcc)减小,以及互连电阻的减小,所以功耗自然就减小了。

历史上,每个节点时代(Technology node/Technology generation)的诞生除了带来Unit cost的变化,还会带来~30%性能的提升,也是通过上面那些功耗和频率等效能计算出来的。

再来讲讲等比例缩小带来的问题:

1) 亚阈值漏电(Subthreshold Leakage):--"Off" is not "Real Off"。等比例缩小,我是不是Vt也一直无限缩小,为啥不是直接就10mV?答案是不可以的,因为Vt越小,有可能带来的问题是亚阈值漏电增加,你会增加Standby current或者Static power consumption,待机时间还能久吗?用着能不发热吗?对吧。

2) Vt roll-off: 短沟管不断,这是短沟道效应,前面有提到就不说了。当然可以通过pocket implant来抑制。

3) 栅极漏电(Gate Leak): GOX减薄自然容易发生隧穿,所以漏电流Ig自然就增大。所以需要提高介电常数,比如N2O氮化。

4) Ion/Ioff trade-off: 这个比较容易理解,刚讲过Vt比较低容易有亚阈值漏电,但是Vt比较低容易得到比较高的Ion,所以到底取Vt比较高好还是比较低好?这真是一个Trade-off的好学问,鱼和熊掌不可兼得。

最后再讲一下摩尔定律的延伸,这现年大家为了摩尔定律太累了,不知道什么时候是个头?现在也该到头了,再不到头马上都要到小于原子直径了,所以都在寻求新的方向。于是有了MtM (More than Moore)。比如2.5D封装和3D封装技术,既然横向没法了,那我就朝空间去发展,甚至有System in Package等等。这确实是个不错的idea,所以这个创意上有了FinFET,把Gate做成竖起来的,这样L减小了,但是Leff增大了,所以抑制了短沟到效应的一系列问题。

Intel自己也不打算一直引领摩尔定律了,这些年跑得很辛苦,所以早在8年前,他们就开始走另外一套定律叫做“Tick Tock”。在每次“tick”周期中,英特尔会引入尺寸更小的制造工艺。而在每次“tock”周期中,英特尔的芯片架构和性能将得到改进。因为设计改善性能远比制造投资小得多,而且也能够为自己gain到时间吧,也许正是因为有了tock的借口,所以Intel在制程的开发上动力不足,快被我们赶超了。

不管怎么样,时代是在进步的,7nm时代也即将来临,新的代沟又要产生了。呵呵~

http://pan.baidu.com/s/1ntFxoyl

发表评论 取消回复