专题-1: Unit Process–Photolithography (转)

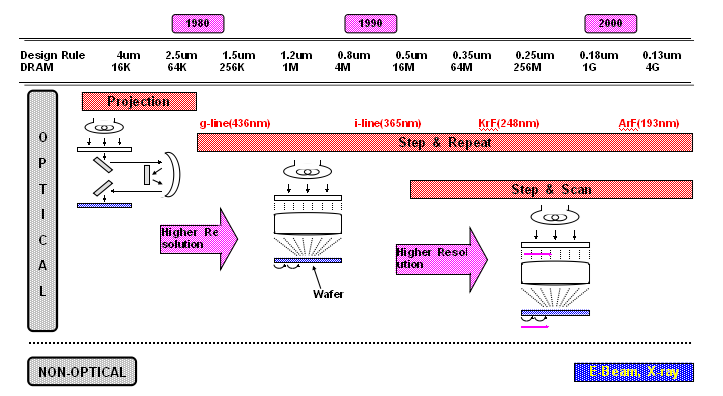

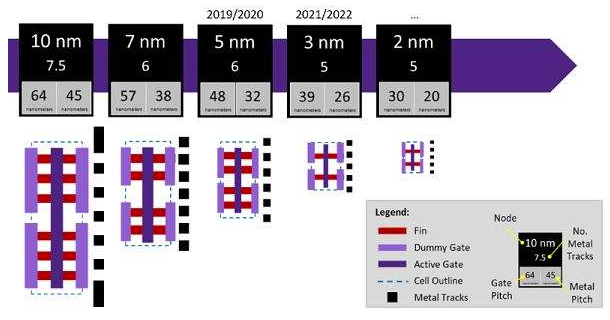

本文转自芯苑,ic-garden.cn (由于芯苑会经常关闭站点,故转载存留) 随着半导体特征尺寸(Moore's Law)下降,需要越来越小的波长得到更小的曝光线宽(大波长容易衍射)。5、6寸时代都是g-line/i-line,8寸开始i-line/DUV了。HMDS是一种蒸汽,在Coat光阻之前必须在HMDS蒸气中熏一会,有助于光阻的表面粘附性(Contact Angle),Coat