近10年来,当集成电路进入亚微米阶段,当人们享受到摩尔定律带来的好处时, 一朵乌云,一直笼罩在集成电路业界的上空,就是越来越严重的跑冒滴漏现象。 作为集成电路的最基本组成单元,晶体管,当尺寸越来越小的时候,漏电缺越来越严重,不仅传统漏电的地方漏,本来不该漏电的地方也开始从涓涓细流满满发展成波涛汹涌。 就像上图的那个漏水的水龙头。

刚开始,漏水的地方主要是出水口和进水口直接的部分, 因为水流主要在这里流动。 慢慢地,水龙头越来做越小,人们发现,主要的漏水的地方从原来的进水口和出水口出,移到了中间用来拧紧水龙头的部分。哪怕你不经常开关水龙头,可这个地方会持续不断地渗水。 如果拆开水龙头来看,出毛病的地方通常是一个橡胶作的皮垫。水龙头尺寸做小了以后,皮垫的尺寸跟着缩小,以至于太薄,水直接从皮垫渗出。 就像这张图:

多垫皮垫解决漏水问题

皮垫太薄导致漏水解决办法是什么?简单,多垫几层皮垫,一层不够两层,两层不够三层。 这样,中间漏水的问题就可以暂时解决了。

用来进行栅极绝缘的绝缘层,一般是用二氧化硅做的,相当于水龙头中的皮垫, 通常只需要一层。 但是,赛灵思的Virtex-2, 用了两层氧化物。从90nm开始赛灵思的Virtex-4,65nm Virtex-5,40nm Virtex-6,都采用了三重氧化物栅极的工艺,降低漏电流,从而达到降低静态功耗的目的, 三重氧化物栅极长得是这个样子滴:

当然,皮垫垫多了,跑冒滴漏解决了一些,可是开关起来肯定不够灵活,因此,这种工艺只是在非关键区域使用,比如用于配置FPGA的地方。 真正需要高速的区域,还是采用一层氧化物工艺。 因此 Virtex-2, 4,5, 6 尽管在降低功耗上做得很出色,可和精心设计的ASIC比,仍然有差距。 毕竟那么多闲置的资源在那里,每个跑冒滴漏一点,数千万个加到一起,就不是小数字。

赛灵思的竞争对手没有用三重氧化物这个方法,而是用统一抬高衬底电压的方法,降低栅和衬底的电压。此方法投机取巧,就像水龙头漏水了,就把总闸关小一点,这样,漏水虽然看上去小了,可是你想用水的时候,流出水的速度也大大降低。体现在性能上,就是所有的管子速度降低。

皮垫太薄了换特氟龙

当集成电路进入28nm节点的时候,尺寸实在是太小了,栅极已经薄到只剩几个原子的厚度,就算是弄上3层,仍然嫌薄, 因此,要另辟蹊径。

水龙头解决这个问题的办法仍然很简单:不用皮垫了,咱换个高防水性的材料,很薄的一层,但就是很管用,比如特氟隆什么的。果然问题圆满解决。

可是问题又来了,特氟隆和龙头中间的铁旋钮连接不太好,怎么办?干脆,吧中间的铁旋钮换成铜的,就解决了。 铜本身比较致密,防水性本来就好,加上特氟隆,效果果然棒极了。

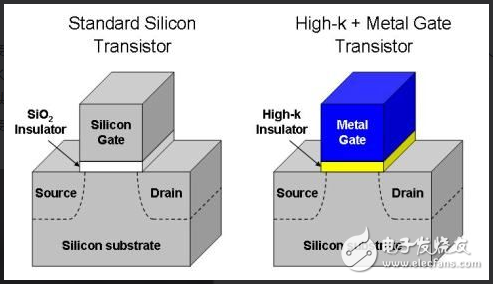

在集成电路中,刚才用水龙头作比喻的高防水性,对应的就是介电常数K,高介电常数,就是所谓的高K,HIGH-K,金属栅极,即是metal gate, 合起来,就是HKMG. 这样,HIGH-K材料+金属栅极, 就完全取代了二氧化硅氧化物+多晶硅栅极。用水龙头作比方,就是特氟隆皮垫加铜旋钮。

这个改变可不得了,革命性的,令人头痛的栅极漏电一下子减少了100倍。要知道,这个栅极漏电乘以晶体管数目永远是个很大的数,是静态功耗的重要组成部分。 这部分的漏电如果减少了100倍,28nm FPGA的容量虽然翻倍了,仍然可以做到功耗减半。

HIGH-K的比较图:

TSMC的艰难研发

HIGH-K这个工艺, INTEL早在45nm这个节点就搞定并采用了, TSMC虽然在芯片代工领域一直做得不错,可比起INTEL,还是差那么一点点。 因此TSMC放弃了在45nm这个节电采用HIGH-K工艺,也使得在这个节点上,甚至没有掌握三层氧化物这样方法的公司被静态功耗奇大无比的某款芯片折磨得抓狂,良率一直无法提高。

尽管如此,TSMC坚持在HIGH-K工艺上的投入,使得它在与其他芯片代工厂在28nm节点的争夺中,开始占据先机。

可编程势在必行

在28nm节点,由于尺寸的进一步缩小,使得需要维持开关的核心电压降低,会降低动态功耗,这是天大的好事,再加上HIGH-K的对栅极静态漏电革命性的减少,使得FPGA 目前的短板 “功耗“,与ASIC相比,有了质的提高, 因此,可以预计,2012年以后,FPGA大行其道,成为电子设计的绝对主流, 实现赛灵思提出的“可编程势在必行“的目标并不仅仅是市场炒作。

学术化语言的版本

喜欢进一步深入研究的,请参阅本文的学术化语言版本,如下:

半导体工艺不断细化的一个显著好处是芯片的动态功耗不断下降。因为可以采用更低的工作电压,此外更小的尺寸有助于减小芯片内部分布电容。但在另一方面,由于 晶体管体积的缩小,包括门极(栅极)泄漏电流以及源-漏泄漏电流在内的静态泄漏却在逐渐增加,因此带来的功耗成了一大顽疾。门极泄漏就是电子穿过阻止其运 动的绝缘层产生的泄漏电流。而在晶体管处于关断状态时,仍会有少量电子从源极向漏极流动,这就是源-漏泄漏。早在2004年,Intel发现因静态泄漏导 致的功耗已占到芯片总功耗的25%。进入65nm之后,随着管子体积的缩小,标准薄氧化层晶体管的静态泄漏急剧增大。为了同时实现高密度和低漏电流,业界 各方面都在不懈努力研究各种减少泄漏电流的方法。一种称为三重门极氧化层(triple-oxide)技术的工艺通过有选择地增加门极氧化层厚度来减少泄 漏电流,同时又不牺牲性能。尽管这三重门极氧化层仍很薄,但这些晶体管的确展现出比标准薄氧化层晶体管更低的漏电流。Intel公司则推出了针对45nm 技术的HK+MG晶体管。所谓HK(High-K)就是采用相对二氧化硅而言具有很高绝缘常数的材料,它可在晶体管的门极和通道间产生一个强大的场效应, 并呈现出很高的电子绝缘特性。采用金属门MG (Metal Gate)还能增强门的场效应。因此,HK+MG组合有助于显著减少漏电流,增加门电容和驱动电流。

赛灵思可编程平台开发全球高级副总裁 Victor Peng 指出:“在 28 纳米这个节点上,静态功耗是器件总功耗的重要组成部分,有时甚至是决定性的因素。由于提高可用系统性能和功能的关键在于控制功耗,因此为了实现最高功效,首先必须选用适合的工艺技术。我们选择了台湾半导体制造有限公司 (TSMC)和三星(Samsung)的高介电层/金属闸 (high-k metal gate)高性能低功耗工艺技术,以使新一代 FPGA 能最大限度地降低静态功耗,确保发挥28 纳米技术所带来的最佳性能和功能优势。”

与标准的高性能工艺技术相比,高性能低功耗工艺技术使得 FPGA 的静态功耗降低了 50%,较低的静态功耗可让赛灵思向客户交付业界功耗最低的 FPGA,且比前代器件的总功耗减少 50%。同时,新一代开发工具通过创新时钟管理技术可将动态功耗降低 20%,而对赛灵思业界领先的部分重配置技术的增强,将帮助设计人员进一步降低33%的功耗和系统成本。

发表评论 取消回复