转自:微信公众号 显示汇,微信号Display_Sea

光刻机分为紫外光源(UV)、深紫外光源(DUV)、极紫外光源(EUV)。按照发展轨迹,最早的光刻机光源即为汞灯产生的紫外光源(UV)。之后行业领域内采用准分子激光的深紫外光源(DUV),将波长进一步缩小到ArF的193 nm。由于遇到了技术发展障碍,ArF加浸入技术成为主流。

想当年整个芯片工业,各家包括intel ,GF, 台积电,三星都在三星都在22nm,28nm这个节点卡了很久,想必是遇到193nm ArF的极限了。

然而193nm能做出50nm以下,1/4波长的尺度,已经非常神奇了不是吗?

不过这背后也存在命名问题。xx nm节点不意味着真正的结构就那么小。首先这个数字原来是指结构的half pitch,即一半的周期。而到了后来水份更多,一般是指最小feature-size。比如一排100nm周期的突起或者凹陷,突起的宽度20nm, 空隙80nm,那么不严格的说这也是一个20nm的工艺。

为什么193nm的ArF光能做出28nm的线?

1、利用光刻胶特性

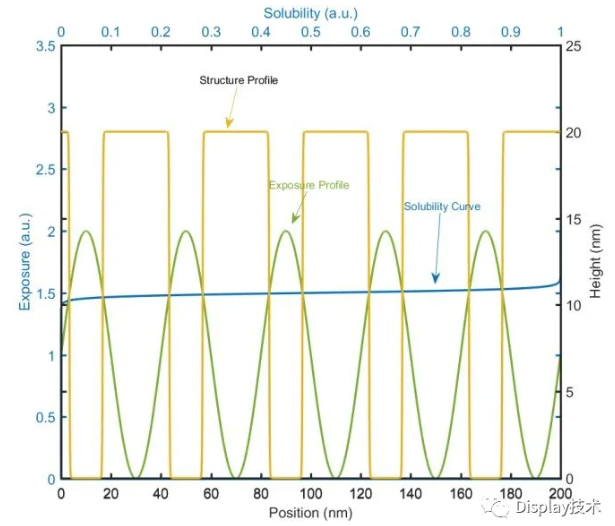

单从光场分布来说,一个峰或谷的宽度很可能还是突破不了衍射极限。但是可以利用光刻胶的性质!

光刻胶曝光后的溶解性依赖于曝光量,这大家都知道,但是这个依赖很不线性。通过控制这种不线性,使得在某个阈值曝光量附近,小一点的完全不会溶解,大一点的极易被溶解,那通过准确把握曝光量,就可以轻松控制最小结构的线宽。

试想一个均匀分布类似正弦波的光场,把曝光将控制到只有波峰附近那些位置能完全溶解,之外的部分溶解性不变,那么最后做出来的结构就是一个周期和正弦波一样,但是最小宽度小的多的结构。

见下图。黄色曲线代表的结构的凹陷要小于光场分布一个峰的宽度。

当然这种方法也不是能做出无限小的Feature。毕竟光刻胶的溶解特性哪儿有想要什么就有什么的,每一种配方的研制都非常复杂,还要和现有的流程工艺匹配。而且光刻胶涂层毕竟是有厚度的,表面的曝光分布和整体也不尽相同。同时它的机械性质也无法维持很窄的细节的完整性。

还有另外一些方法能将光刻胶层被激活的区域集中在比曝光光场小很多的尺度内,包括各种玄乎的化学处理,热处理等。

2、SADP多次曝光工艺(LELE、LFLE)

既然有了上述方法,能让Minimum Feature Size至少小于半周期,那么接下来实现密度的增长就有了可能——通过多次曝光。

同样的结构,平移一下再做一遍就多了一倍的密度。

但是实施起来并没有那么简单。

关键就是在后续曝光中要做到一个对先前结构保护冻结的步骤。最朴素的多重曝光技术就是,做一次,再做一次,可以称作LELE(Litho-Etch-Litho_Etch)。如下图

最上面是已经经过一次Patterning的保护层(藕荷色,如SiN)再加上一层光刻胶(紫色)。光刻胶在新的Mask下被刻出另一组凹槽(中间)。最后光刻胶层被去掉,留下可以进一步蚀刻的结构(下图)。

另外一个变种是Litho-Freeze-Litho-Etch (LFLE).

第二层光刻胶直接加在第一层没被去除但被化学冻结的光刻胶上,再来一次光刻,形成两倍的结构。比LELE可以节省些步骤。

这一类多重曝光的特点就是流程简单粗暴,很早就有人尝试应用。但一个最大的问题就是,后一次光刻和前一次的对准问题。

这几乎是一个可以让这类方法彻底无效的巨大难关。

想要做出20nm左右的结构,那对准误差要控制在4-5nm以下,然而可以用于实施观察的SEM分辨率最好也就10nm!

总之这个问题确实阻碍了这种方法的应用——除了早期45nm、32nm节点的DRAM工艺(结构简单,重复性高),而且超光双重曝光的情况几乎没有,CPU GPU芯片应该采用的并不多。接下来是另一类聪明一点的多重曝光,可以统称为SADP (Self-Aligning Double Patterning).

比如Side Wall Transfer就是核心的实现方式。主要是利用第一层结构的Sidewall来形成两倍的Feature, 从流程上来说省了不少事儿,而且不用考虑对准的问题。

以上所述的各种方法,结合实际来看,由于真实的集成电路结构超级复杂,各种不同材料,不同区域,不同的互联和切断的要求,而且实际的布局是需要二维甚至三维考量的,所有这些复杂因素就构成了更多更多的难题,和捷径,由此衍生了基于不同材料(电介质层,金属)和不同功能区域的奇技淫巧。但是这块太复杂了,我也不甚了解。

3、光学数值孔径NA

说了这么多怎么通过光刻之后的手段来增加密度减少线宽的,但还需要一个最核心的技术——如何把老老实实的单次曝光的Feature/周期做的最小最漂亮呢?

基于CD=k*lamda/NA, k通常为一个0.25-1之间的常数,那么首先想能提高的就是NA=nsin(像方半孔径角)。正弦最高做到1,而在物镜和晶圆之间加一层高折射率液体,比如水,NA就到了1.33。(应该也可以用更高折射率的油到1.4多?)。

Immersion Lithography,不多说了,EUV之前妥妥的必备技术(然而到了EUV肯定用不了了)。然后就是Off-Axis Illumination。让光学系统的主光轴和照明方向不一样,光源斜着打。

这个原理也比较直观,就是尽可能的舍弃一些MASK的空间低频成分,让含有更精细结构的高频成分进入物镜从而成像。从原理上来讲,MASK上凡是小于光照波长的高频成分,都成为了高频信息,所对应的光是只在横向传递,而轴向极具衰减的隐失波,很大可能没有办法被物镜收集。斜照明的情况下,高频空间成分正负至少有一支有更小的衍射角从而进入物镜,甚至从隐失波变成可以被收集的成分(当然 另外一支就被推的更远了,不过无所谓)。最后的效果就是Wafer上的像含有更多的高频成分,自然也就更接近Mask的形态。

这个过程是怎么实现的?

我也不知道,但想必需要非常复杂的波动光学模拟方法以及无数次的实验反馈及后续优化。从某些角度讲,OPC这一领域好像是当前FAB前沿最吃香的工作(纯属道听途说,准确性不保证)。

小结

这个技术的形成离不开两个主要的突破。第一个突破是浸液式光刻,即是将水放在晶圆和镜头之间。第二个突破是多重成像,即是将一层成像的过程分解成两步或多步。比如,要制作一组距离非常靠近的洞,一个晶片需要在光刻机中处理一次,加工成品的一半,接着再重复一次,少许错位后,加工另一半。因为晶圆的定位可以做到很高精度,所以工程师们可以完成比之前一步成像下间距更小的成像。从原理上说,成像步数越多,成像越精密。但是每增加一步,就会使芯片制造成本变得更加高昂,程序更加复杂。

续(7nm以下工艺)

当前发展已经进入7nm,5nm时代,显然再怎么改进ArF光的生产工艺是无法做到的(业内公认极限为11nm),所以就产生了EUV光(极紫外光)。

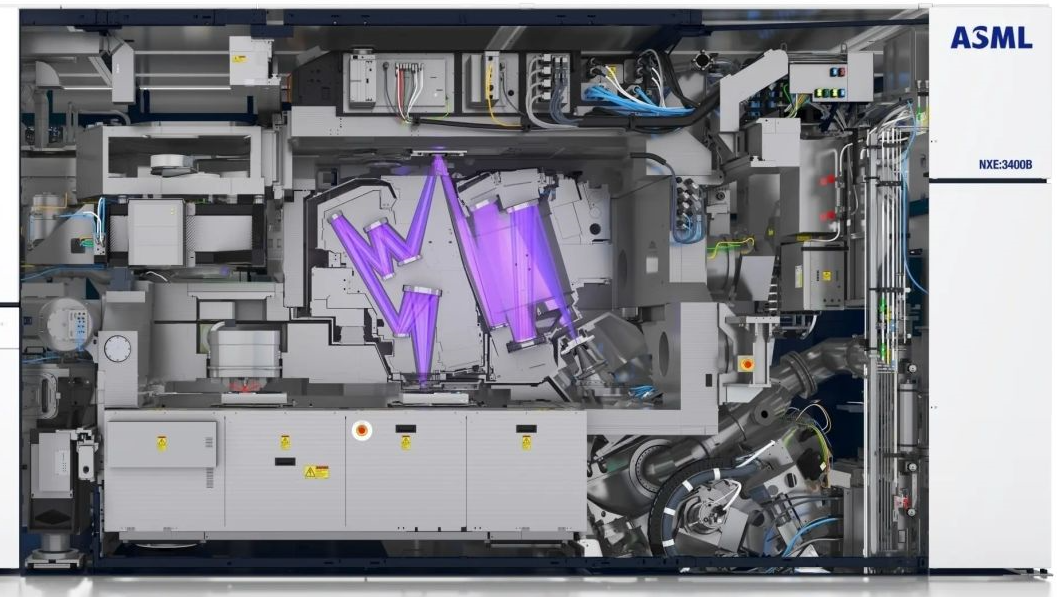

为了提供波长更短的光源,极紫外光源(EUV)为业界采用。目前主要采用的办法是将二氧化碳激光照射在锡等靶材上,激发出13.5 nm的光子,作为光刻机光源。目前仅有由荷兰飞利浦公司发展而来的ASML(阿斯麦)一家可提供可供量产用的EUV光刻机,因此ASML对于EUV光刻机的供货重要性不言而喻,同时一台EUV光刻机也是价值不菲。

EUV光的收集难度极大,因此转化效率也很低,这也是为什么EUV如此耗电的原因之一。这种光非常容易被吸收,连空气都不透光,所以整个生产环境必须抽成真空;同时,也无法以玻璃透镜折射,必须以硅与钼制成的特殊镀膜反射镜,来修正光的前进方向,而且每一次反射仍会损失 3 成能量,但一台 EUV 机台得经过十几面反射镜,将光从光源一路导到晶圆,最后大概只能剩下不到 2%的光线。反射镜的制造难度非常大,精度以皮米计(万亿分之一米),如果反射镜面积有德国那么大(大概是山东、河南两省面积之和),最高的突起不能超过1厘米。

“摩尔定律”指出:1、集成电路芯片上所集成的电路的数目,每隔18个月就翻一番;2、微处理器的性能每隔18个月提高一倍,而价格下降一半;3、用一美元所能买到的计算机性能,每隔18个月翻两番 。所以目前认为EUV是摩尔定律的续命之作。

Si原子直径为0.117nm,那后续刻蚀工艺的极限又是多少呢?留给大家遐想!!!

发表评论 取消回复