芯片制造工艺

芯片制造工艺问答027:Gate oxide对产品影响的参数有哪些?

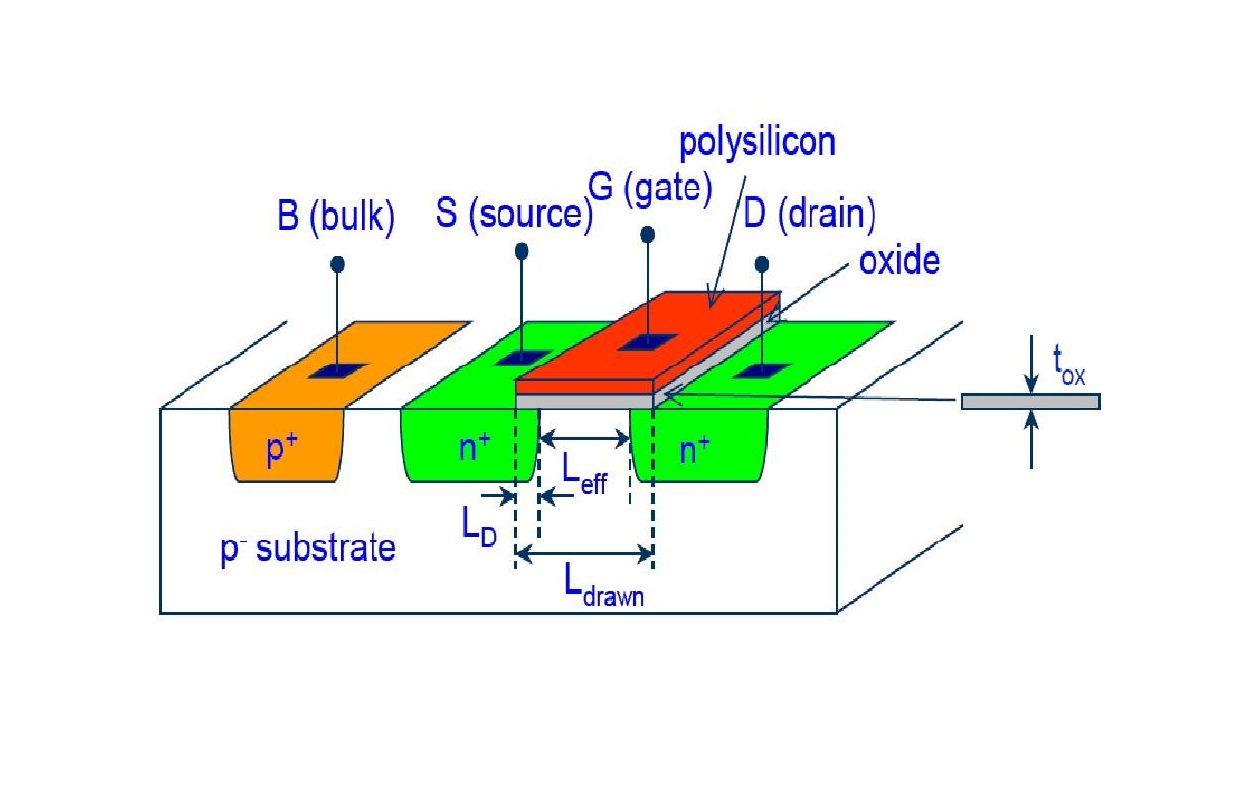

MOSFET(以下简称MOS管)是集成电路芯片的基本组成单元之一,由金属(M)-氧化物(O)-半导体(S)组成。如今Gate材料多用多晶硅(Poly-Si)材料了,为了进一步降低中间氧化层的厚度也用上了HfO2等High-K材料,不过大家还是习惯称其为MOS管。一个典型的MOS管有三个端子,即栅极(Gate)、源极(Source)和漏极(Drain)。MOSFET的操作原理并不复杂,简单来说就是一

芯片制造工艺问答025:N-well implant打入P31, 120KeV. 请估计光阻厚度最少应有多厚?

Ans 一般光阻厚度必须至少等于离子植入Projection range (Rp) 加上四倍的 Projected standard deviation (DRp),

usually define PR thickness as 0.0001% transmission, from data table: P31 @Energy = 120keV, PR masking

material thic

芯片制造工艺问答024: Vt IMP的目的为何? 对产品电性有何影响?

Ans Vt implant is used to adjust threshold voltage

of transistors, useful in CMOS Vt matching and device current adjusting. Since

it is quite shallow, it can be used without seriously degrading of sub

芯片制造工艺问答023:Sacrificial oxide (SAC oxide) 的目的为何?

Ans Sacrificial oxide was succeeded after SIN-Remove

of both LOCOS and STI process integration, the basic purposes are:Eliminate the defects caused by Kooi Effect (去除在field oxidation过程中, 所产生的white

rib

芯片制造工艺问答022:热磷酸对Si3N4, Oxide的蚀刻率分别是多少? 蚀刻率可控制因子为何?

Ans 50:1 HF E/R 53+-5A/min of SiOxNy = 120~150A, 220sec

to etch 175A SiOxNyH3PO4 E/R is 60+-6A/min for SIN, 1.5 A/min ~0.25

A/min for oxide, for new H3PO4 acid the [Si] is low and oxide E/R is high bu

芯片制造工艺问答021:去除Si3N4时, 为何要在热磷酸之前加50:1 HF蚀刻? 此蚀刻时间太短有何影响?

Ans 50:1 HF is designed to remove any oxide above

SIN before H3PO4 strip. If HF etch time is too short, the oxide above SIN will

not completely removed, and SIN can not be stripped by H3PO4 and result

芯片制造工艺问答020:总共有多少种光阻去除方式? 个别适用于何种情况?

Ans For FAB* stripping process, clear functions layout

are designed by machines & process layers, which are simply described as

below:(1)Dry ashing:M/CTotal recipe

No.Function designProcess laye

芯片制造工艺问答019:ODR光罩和OD光罩有何关系? 试画图解释之.

Ans ODR之用途在于减少CMP时之loading effect. ODR和OD光罩之关系式如下: ODR(121)=(((120

sizing –0.4) sizing 0.4) sizing –0.2)if

OD< 0.4um OD (yellow color) will be regarded as