“芯”无远虑,必有近忧 ----FD-SOI与FinFET工艺,谁将接替Bulk CMOS?

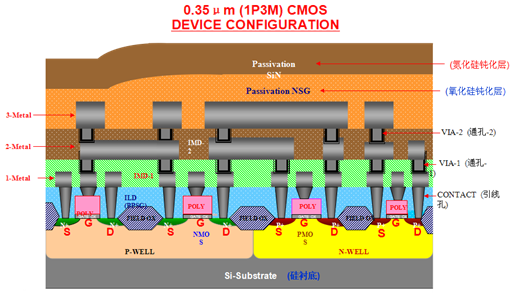

“传统Bulk CMOS工艺技术将在20nm走到尽头,必须用创新的思路和方法寻找新的替代工艺。”----IBS主席兼 CEO Handel Jones现在,大量IC采用体硅CMOS(Bulk CMOS)工艺技术实现,这是一种制造成本低、性能较高和具备不错低功耗性能的成熟技术,但是,当工艺节点升级到20nm左右时,Bulk CMOS将无法获得等比例缩小的性能、成本和功耗优势,很多业者认为B