Diffusion

栅极介质层的变迁(Gate Dielectric) (转)

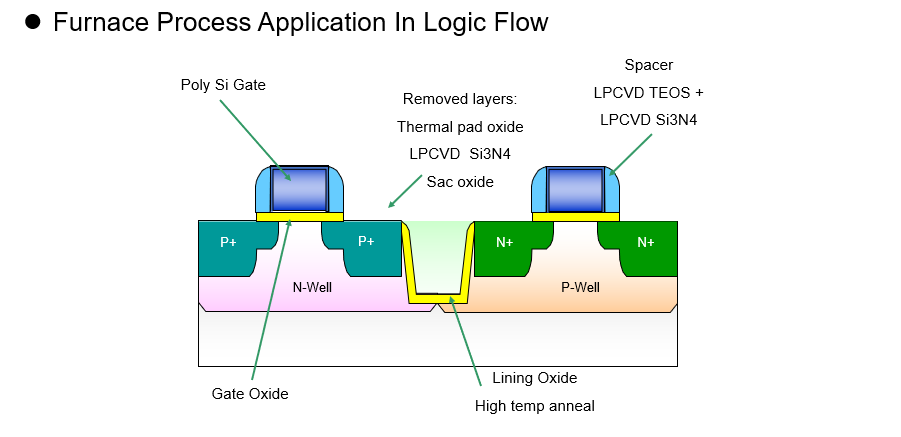

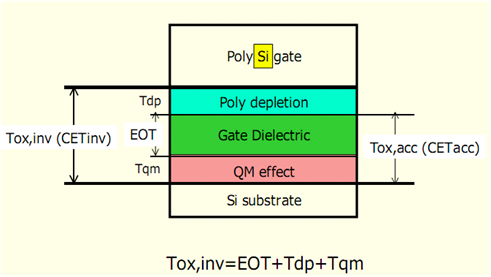

本文转自芯苑,ic-garden.cn (由于芯苑会经常关闭站点,故转载存留)昨天已经讲完了栅极材料的演变(Gate Electrode),当然伴随它一起的自然就是栅极介质层(Gate Dielectric),记住我讲的是栅极介质层,不是我们平常讲的栅极氧化层(Gate Oxide),早期我们讲的MOSFET的介质层就是我们狭义讲的Oxide,但是随着Moore's Law的scale down,

芯片制造工艺问答014:SiN CVD dep时炉管各部分的温度别控制在什么范围? 为什么如此?

Ans Temperature control divided to three zone:

bottom, center, upper, since gas flow from bottom, in order to compensate the

difference of gas concentration, B-zon

芯片制造工艺问答031:Gate oxide厚度如何Monitor? 其量测误差为何? 在线如何控制厚度保持定值?

Ans Gate oxide厚度Monitor: 每个RUN需将控片(C/W)与产品芯片一起进炉管, 控片(C/W)分别摆放在上, 中, 下位置. 在oxidegrowth后以椭圆测厚仪(ellipsometer)测量thin oxide thickness.Within wafer uniformity: (芯片内九点之MAX-MIN) / (2×九点之平均值)Wafer to wafe

芯片制造工艺问答030:Gate oxide 前制程B-Clean的目的为何? 其中的APM dip time会影响什么产品参数?

Ans Remove Si surface particles, metal Ion, organic,micro-roughness and native Oxide. --> Use 22220A,where SPM (CR) 1min to remove light organic, 100:1 HF 3min to remove any nativeoxide, and AP

芯片制造工艺问答027:Gate oxide对产品影响的参数有哪些?

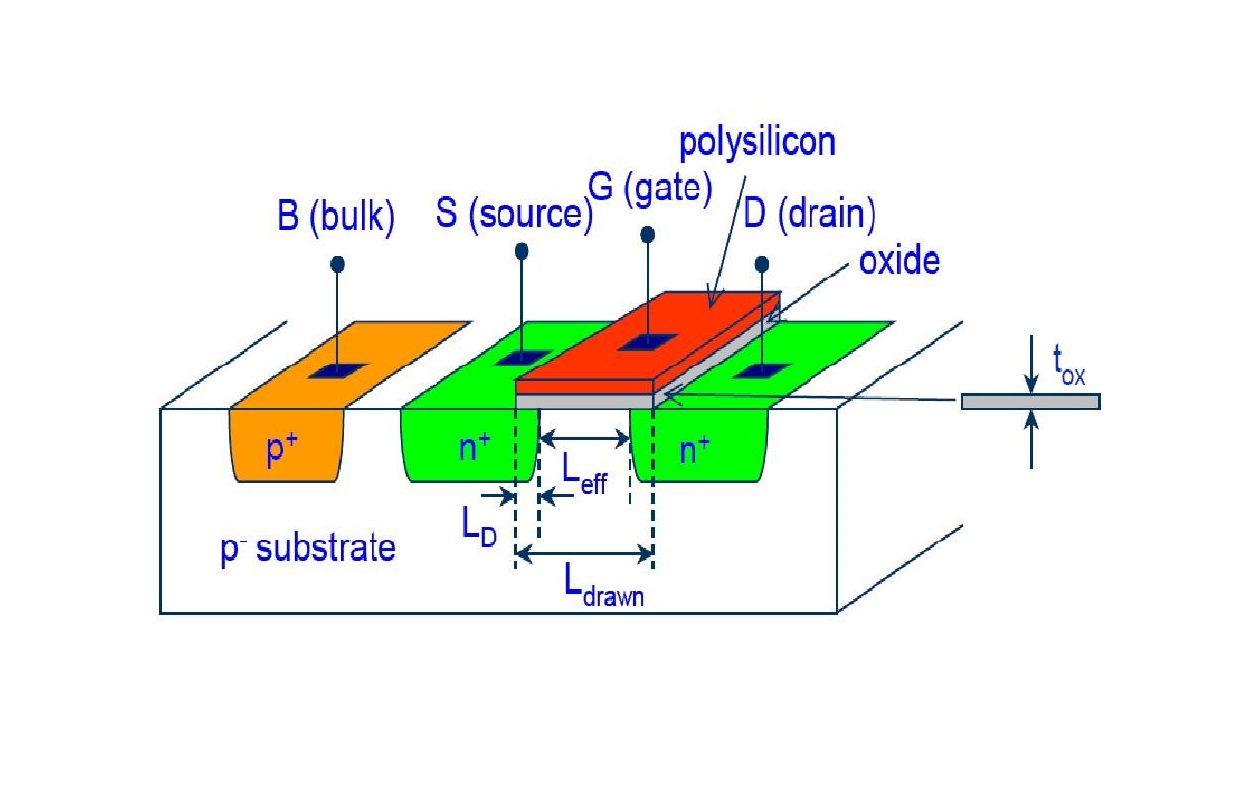

MOSFET(以下简称MOS管)是集成电路芯片的基本组成单元之一,由金属(M)-氧化物(O)-半导体(S)组成。如今Gate材料多用多晶硅(Poly-Si)材料了,为了进一步降低中间氧化层的厚度也用上了HfO2等High-K材料,不过大家还是习惯称其为MOS管。一个典型的MOS管有三个端子,即栅极(Gate)、源极(Source)和漏极(Drain)。MOSFET的操作原理并不复杂,简单来说就是一