Gate

功率半导体和5G的新宠-《GaN和SiC》:Part-2 (转)

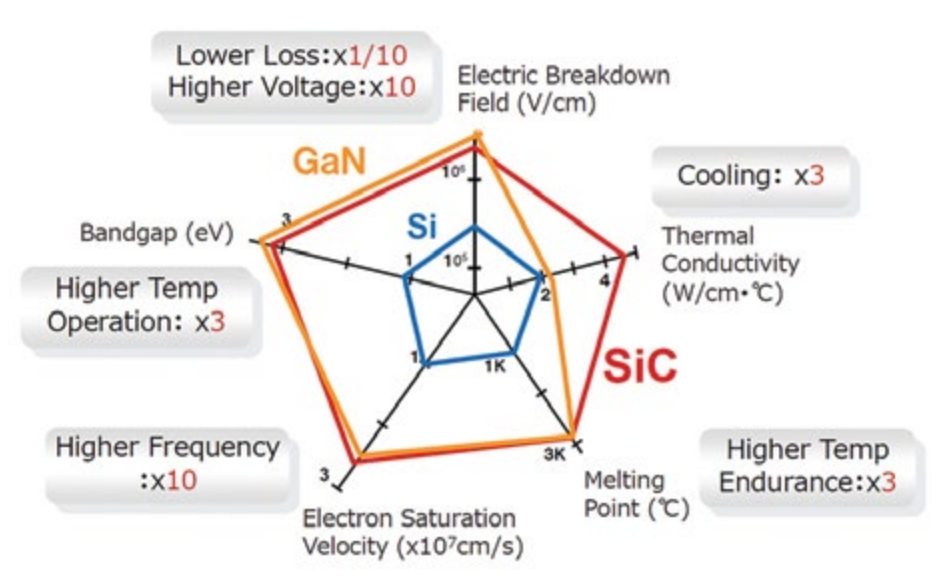

本文转自芯苑,ic-garden.cn (由于芯苑会经常关闭站点,故转载存留)才讲完SiC和GaN的一些概论,赶快乘热把器件工作原理都讲完吧,不然又该落下了。再次谢谢给我鼓励和给我资料的朋友们。从上一份总结里面已经说明SiC和GaN都是宽禁带半导体材料,而且禁带宽度都几乎是Silicon的三倍,所以都非常适合功率器件,而且饱和载流子速度都几乎是硅的10倍,所以他们都非常适合做High freque

IGBT理论与实践–实用篇 (转)

本文转自芯苑,ic-garden.cn (由于芯苑会经常关闭站点,故转载存留)之前发了一篇关于IGBT的文章--“大功率器件-《从PowerMOS到IGBT》”,今年一下子火了。所以趁热打铁吧,继续来点干货吧。资料比较零散,想到哪写到哪,但是绝对没有废话。实在是工作生活都很忙,没时间搞那些排版什么的,大家将就看了啊。回顾一下IGBT的工作原理,首先Gate控制MOSFET导通,产生Drain-to

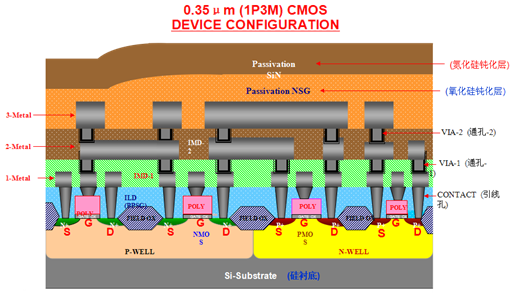

CMOS器件历史浅析–扫盲版 (转)

本文转自芯苑,ic-garden.cn (由于芯苑会经常关闭站点,故转载存留)编者注:这个只适用于没有基础的common course,如果大家了解的话直接跳过,不过可以简单看看发展史吧。上一章节我们讲过BJT Device,如果大家还记得的话,它应该电流工作型器件,而且是双载流子(Hole/Electron)同时工作的。所以它通常用于电流或功率放大型,或者用于高速器件(ECL: Emmitter

如何查Vt shift的Case?MOSFET开启电压(Vt)的制程因素!(转)

本文转自芯苑,ic-garden.cn (由于芯苑会经常关闭站点,故转载存留)很久没有写文章了,客观原因是电脑坏了,主观原因是不知道写什么。类似我们的学习,我们很想好好学习,很想像某人一样功成名就,每个人都是上进的,科学的方法和明确的计划才是最重要的。看来我的反思如何把《芯苑》走的更远,希望大家能够给我些建议,我自己蠢就得求助你们!好了,先把今天的课题讲完吧,前面很长一段时间都在讲栅极 (栅极材料