芯片制造工艺问答027:Gate oxide对产品影响的参数有哪些?

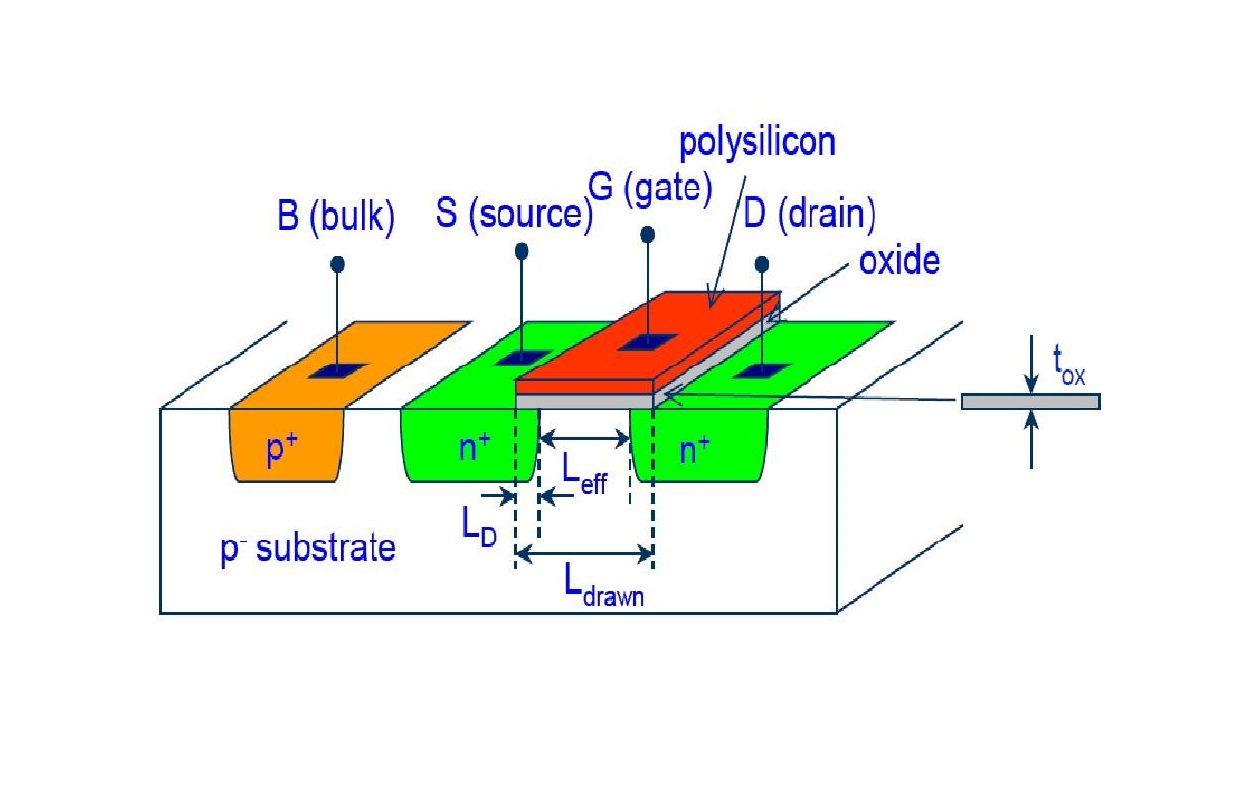

MOSFET(以下简称MOS管)是集成电路芯片的基本组成单元之一,由金属(M)-氧化物(O)-半导体(S)组成。如今Gate材料多用多晶硅(Poly-Si)材料了,为了进一步降低中间氧化层的厚度也用上了HfO2等High-K材料,不过大家还是习惯称其为MOS管。一个典型的MOS管有三个端子,即栅极(Gate)、源极(Source)和漏极(Drain)。MOSFET的操作原理并不复杂,简单来说就是一