GateOxide

半导体集成电路PIE常识

1.何谓PIE? PIE的主要工作是什幺?答:Process Integration Engineer(工艺整合工程师), 主要工作是整合各部门的资源, 对工艺持续进行改善, 确保产品的良率(yield)稳定良好。2.200mm,300mm Wafer 代表何意义?答:8吋硅片(wafer)直径为 200mm , 直

栅极介质层的质量评估 (GOI) (转)

随着MOSFET的尺寸越来越小,栅极介质层的厚度也是越来越薄。作为MOSFET的核心,Gate OXide的可靠性一直都是最主要的制约器件是否可以量产的因素之一。前面我们几乎讲完了Gate Electrode和Gate Dielectric两个部分,今天我们该趁热打铁把Gate Dielectric的可靠性讲完,其实就是我们FAB里面经常讲的GOI测试。

可靠性系列-Gate Oxide Degradation

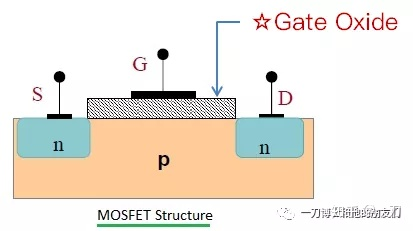

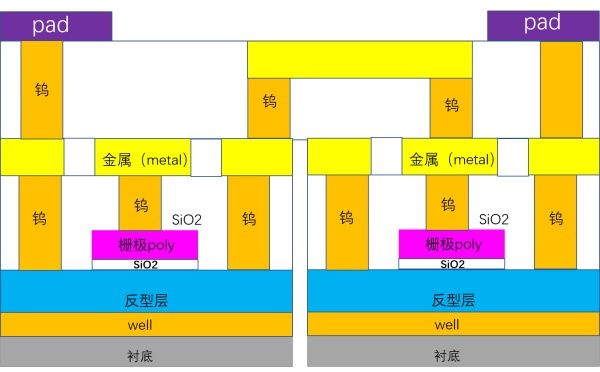

可靠性系列文章将主要介绍可靠性相关的概念及失效机理。01 MOS(Metal-Oxide-Semiconductor)MOSFET(以下简称MOS管)是集成电路芯片的基本组成单元之一,由金属(M)-氧化物(O)-半导体(S)组成。如今Gate材料多用多晶硅(Poly-Si)材料了,为了进一步降低中间氧化层的厚度也用上了HfO2等High-K材料,不过大家还是习惯称其为MOS管。一个典型的MOS管有

如何巧用C-V曲线来查Case(转)

随着半导体制程越来越复杂,我们最关键的参数Vt的控制越来越重要,有的时候我们的Vt如果单纯是衬底浓度影响我们自然可以通过长沟和短沟以及NMOS和PMOS是否同时变动来确定是否是GOX还是Vt_IMP的问题,其实这也是一种correlation它其实是一种逻辑思考方式,只是他是基于理论的。不像现在很多年轻的工程师直接从wafer start直接丢到系统里run到WAT,也能找到问题,可是那不是工程师

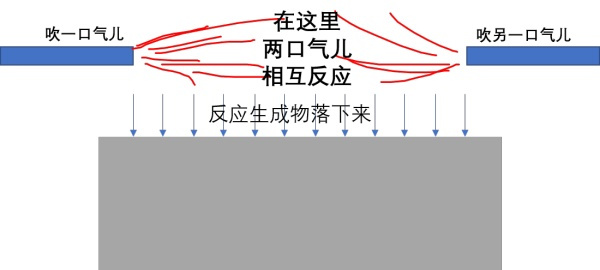

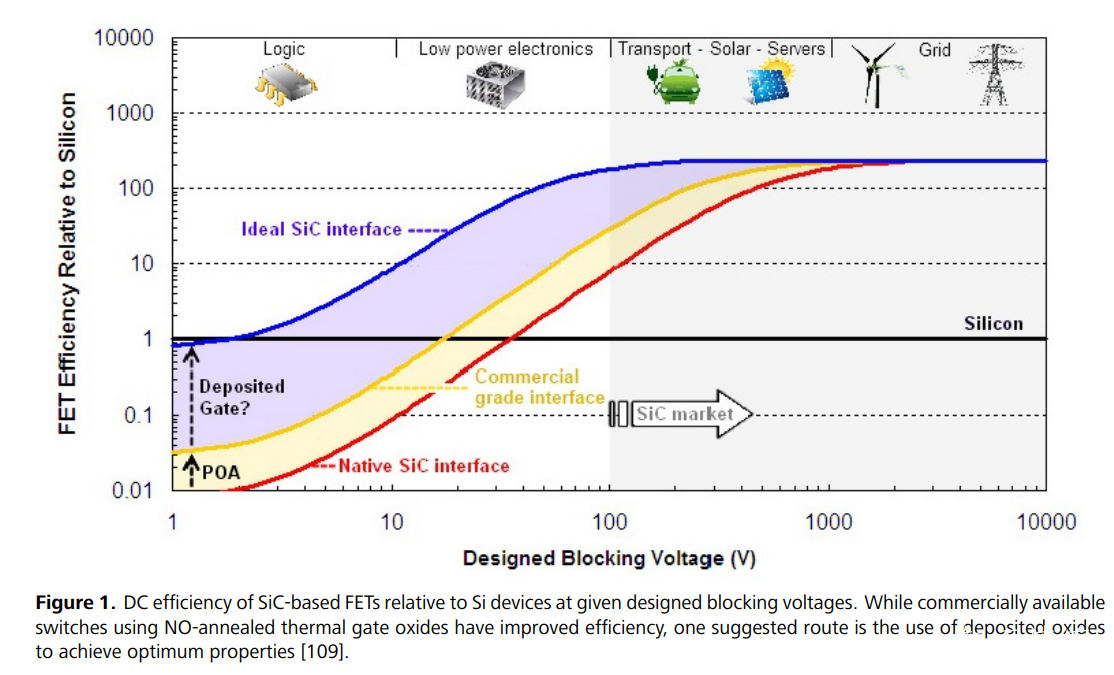

关于碳化硅SiC栅氧(Gate Oxide)以及NO 退火

1. Introduction 我们生活在一个能源匮乏的世界,在这个世界上,工业化和全球化已经成为一种趋势加速了对资源的需求,现在大约每40年翻一番。今天,我们消耗约18太瓦(18×1012瓦),相当于970亿桶原油每年加油。而可再生能源提供了一种环保的替代能源化石燃料仅占总量的10%左右[64]。伴随着清洁能源,必须努力抑制消费,这在一定程度上

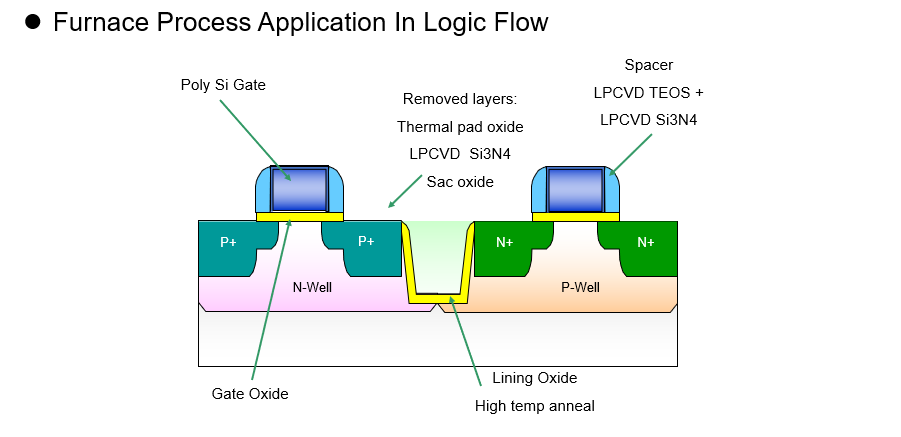

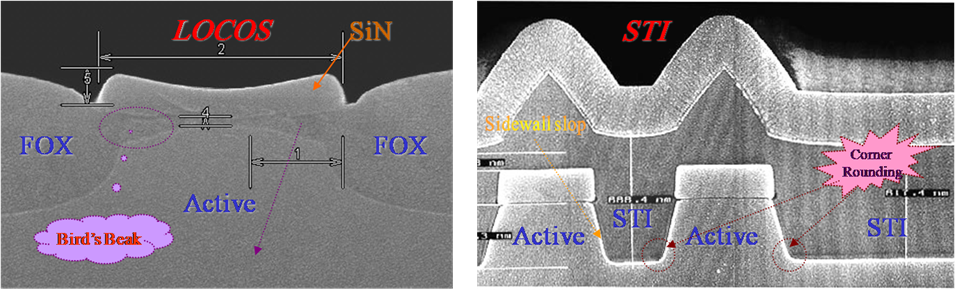

《LOCOS与STI》你真的知道吗?(转)

本文转自芯苑,ic-garden.cn (由于芯苑会经常关闭站点,故转载存留)我们的CMOS制程就是做出NMOS和PMOS,再复杂的电路对我们FAB来讲也就是NMOS+PMOS,那我们总不希望这两个MOS之间互相漏电吧,所以MOSFET之间的隔离技术应运而生。以前我给学员们讲课总是会直观的说,我们的MOS为有源器件(因为需要有两个电压才可以工作,一个叫工作电压一个叫控制电压),那有源器件所在的区域

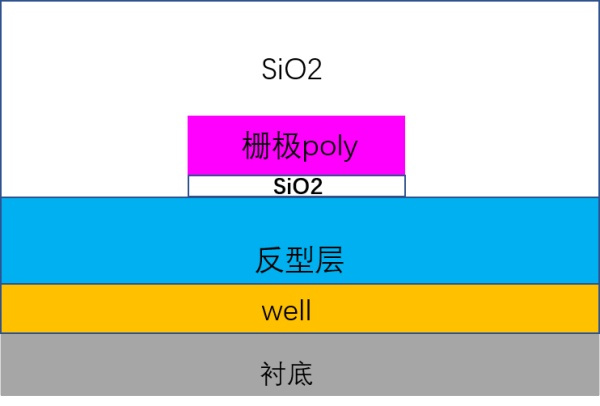

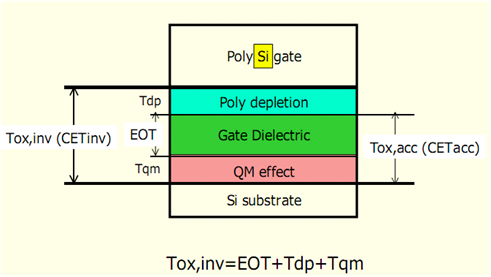

栅极介质层的变迁(Gate Dielectric) (转)

本文转自芯苑,ic-garden.cn (由于芯苑会经常关闭站点,故转载存留)昨天已经讲完了栅极材料的演变(Gate Electrode),当然伴随它一起的自然就是栅极介质层(Gate Dielectric),记住我讲的是栅极介质层,不是我们平常讲的栅极氧化层(Gate Oxide),早期我们讲的MOSFET的介质层就是我们狭义讲的Oxide,但是随着Moore's Law的scale down,

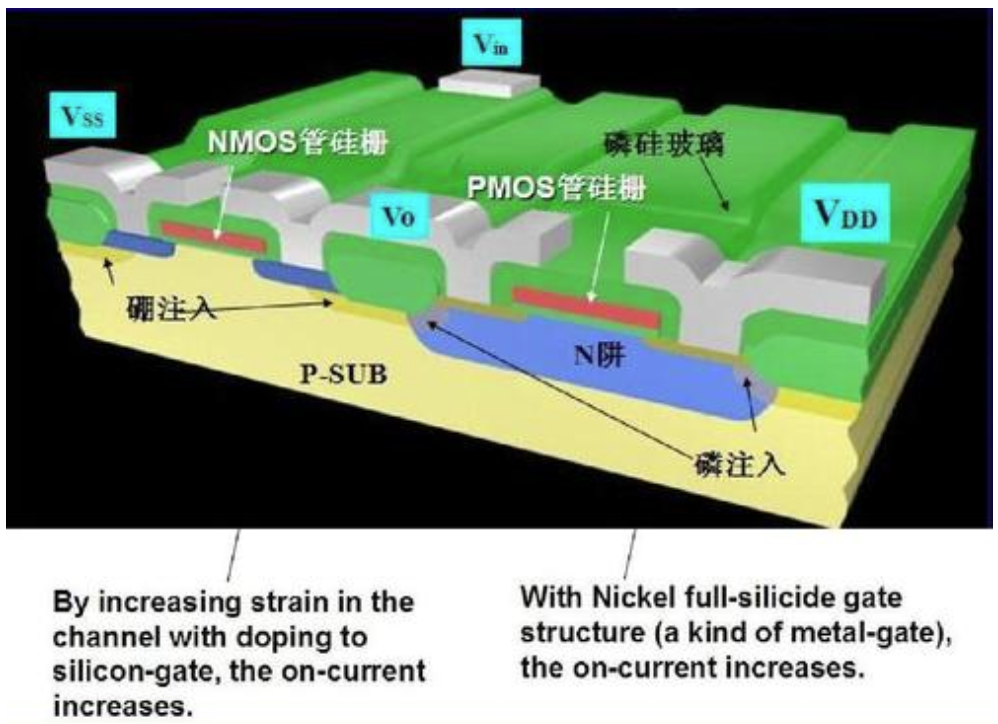

CMOS到底是怎么工作的 ?

在现代集成电路设计中,CMOS(Complementary Metal Oxide Semiconductor,互补金属氧化物半导体)是最基本的单元,我们在新闻中经常会遇到这样的描述“在这个1平方厘米的芯片上,集成了10亿个晶体管”,其中一个最基本的CMOS就是一个晶体管。我们这一期就了解一下关于CMOS的工作原理。由于CMOS是一个比较复杂的一部分,所以我只是从原理上来和大家聊,不涉及到任何物理