所谓的High K工艺用的是什么?

请问各位大神知道High-K和Low-K最新的制作工艺主要是用什么工艺么?PVE?ECD?我看last Gate工艺流程的提到的离子注入用的具体又是什么方法?为什么由于离子注入,first Gate工艺流程中的Gate contact会受到加热,从而影响性能?另外我记得好像一两年前High-K和Low-K还是不能做到一个芯片里的,虽然把他们一起运用理论上会得到更好的性能,但是我想不起当时看到的说的究竟是什么原因导致他们不能做到一起了,有大神知道么?另外这它们现在可以做到一起了么?能的话是因为有什么工艺上的突破么?

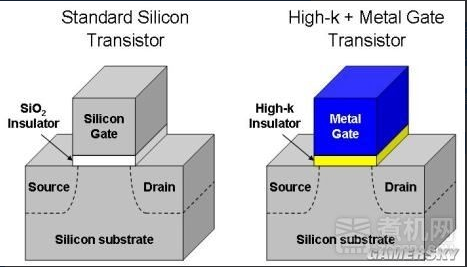

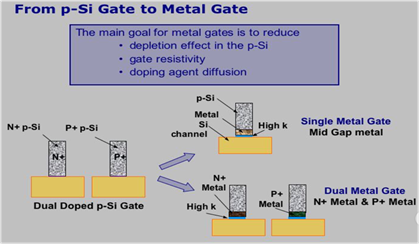

High-k一般指的是gate dielectric部分,也就是常说的栅氧化层或者栅介质层。gate first 与 gate last指的是metal gate (金属栅)的制造顺序。就现在的工艺而言,high-k gate dielectric都是和metal gate一起使用的。

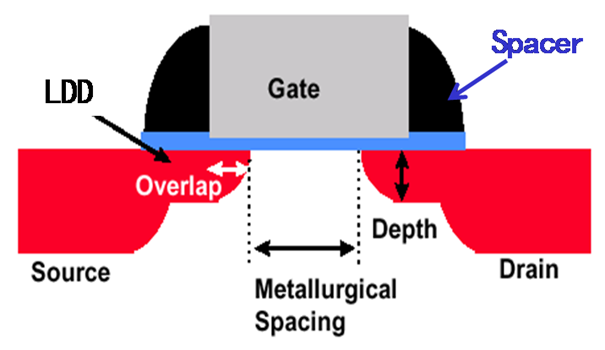

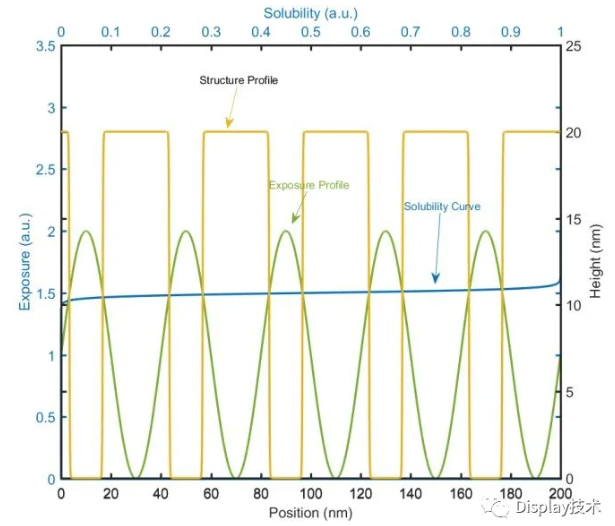

gate first是和传统poly-silicon gate的工艺顺序类似,直接把poly-silicon gate替换为metal;按照正常的工艺流程,其后需要就行源漏离子注入,并进行高温退火以激活掺杂并修复缺陷。由于这个高温退火(一般在1000C以上),限制了前面金属栅只能使用高熔点的材料。

gate last的话,在源漏注入之前,和传统工艺一样,先形成poly-silicon gate。在源漏形成以后,再把poly-silicon gate替换为metal gate。因此没有高温退火的问题,可以使用的金属材料选择范围更广(可以基于功函数考虑选择合适的金属。)

至于low-k,如楼上所说,一般指BEOL工艺金属互连之间的介质层,与前端是否使用high-k gate dielectric没什么关系。

二氧化铪(HfO₂)是一种具有宽带隙和高介电常数的陶瓷材料,近来在工业界特别是微电子领域被引起极度的关注,由于它最可能替代目前硅基集成电路的核心器件金属氧化物半导体场效应管(MOSFET)的栅极绝缘层二氧化硅(SiO₂),以解决目前MOSFET中传统SiO₂/Si结构的发展的尺寸极限问题。

发表评论 取消回复